# COMPLETE DIGITAL DESIGN A COMPREHENSIVE GUIDE

A COMPREHENSIVE GUIDE TO DIGITAL ELECTRONICS AND COMPUTER

MARK BALCH

# **COMPLETE DIGITAL DESIGN**

# COMPLETE DIGITAL DESIGN

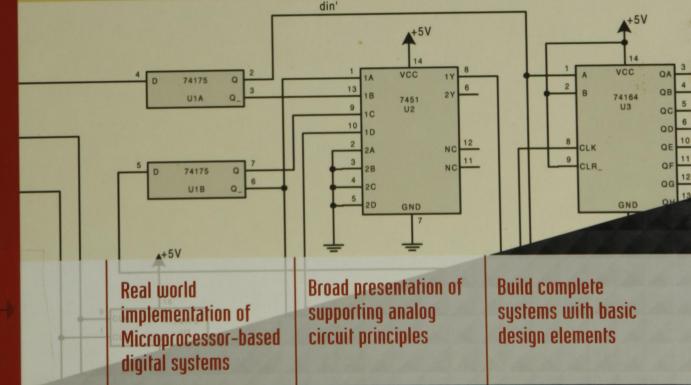

# A Comprehensive Guide to Digital Electronics and Computer System Architecture

**Mark Balch**

# **McGRAW-HILL**

New York Chicago San Francisco Lisbon London Madrid Mexico City Milan New Delhi San Juan Seoul Singapore Sydney Toronto

#### Library of Congress Cataloging-in-Publication Data

Balch, Mark.

Complete digital design : a comprehensive guide to digital electronics and computer system architecture / by Mark Balch.

p. cm.

Includes bibliographical references and index.

ISBN 0-07-140927-0

1. Digital electronics. 2. Computer architecture. I. Title.

TK7868.D5B37 2003

621.81-dc21

2003046465

Copyright © 2003 by The McGraw-Hill Companies, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1 2 3 4 5 6 7 8 9 0 DOC/DOC 9 8 7 6 5 4 3

ISBN 0-07-140927-0

The sponsoring editor for this book was Steve Chapman and the production supervisor was Pamela A. Pelton. It was set in Century Schoolbook by J. K. Eckert & Company, Inc.

Printed and bound by RR Donnelley.

This book is printed on recycled, acid-free paper containing a minimum of 50% recycled, de-inked fiber.

McGraw-Hill books are available at special quantity discounts to use as premiums and sales promotions or for use in corporate training programs. For more information, please write to the Director of Special Sales, Professional Publishing, McGraw-Hill, Two Penn Plaza, New York, NY 10121-2298. Or contact your local bookstore.

041 PG1 701

Information contained in this work has been obtained by The McGraw-Hill Companies, Inc. ("McGraw-Hill") from sources believed to be reliable. However, neither McGraw-Hill nor its authors guarantee the accuracy or completeness of any information published herein, and neither McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

# CONTENTS

Preface xiii Acknowledgments xix

# PART 1 Digital Fundamentals

- 1.1 Boolean Logic / 3

- 1.2 Boolean Manipulation / 7

- 1.3 The Karnaugh map / 8

- 1.4 Binary and Hexadecimal Numbering / 10

- 1.5 Binary Addition / 14

- 1.6 Subtraction and Negative Numbers / 15

- 1.7 Multiplication and Division / 17

- 1.8 Flip-Flops and Latches / 18

- 1.9 Synchronous Logic / 21

- 1.10 Synchronous Timing Analysis / 23

- 1.11 Clock Skew / 25

- 1.12 Clock Jitter / 27

- 1.13 Derived Logical Building Blocks / 28

##

- 2.1 The Integrated Circuit / 33

- 2.2 IC Packaging / 38

- 2.3 The 7400-Series Discrete Logic Family / 41

- 2.4 Applying the 7400 Family to Logic Design / 43

- 2.5 Synchronous Logic Design with the 7400 Family / 45

- 2.6 Common Variants of the 7400 Family / 50

- 2.7 Interpreting a Digital IC Data Sheet / 51

####

- 3.1 The Digital Computer / 56

- 3.2 Microprocessor Internals / 58

- 3.3 Subroutines and the Stack / 60

- 3.4 Reset and Interrupts / 62

- 3.5 Implementation of an Eight-Bit Computer / 63

- 3.6 Address Banking / 67

- 3.7 Direct Memory Access / 68

- 3.8 Extending the Microprocessor Bus / 70

- 3.9 Assembly Language and Addressing Modes / 72

#

- 4.1 Memory Classifications / 77

- 4.2 EPROM / 79

- 4.3 Flash Memory / 81

- 4.4 EEPROM / 85

- 4.5 Asynchronous SRAM / 86

- 4.6 Asynchronous DRAM / 88

- 4.7 Multiport Memory / 92

- 4.8 The FIFO / 94

# Chapter 5 Serial Communications......97

- 5.1 Serial vs. Parallel Communication / 98

- 5.2 The UART / 99

- 5.3 ASCII Data Representation / 102

- 5.4 RS-232 / 102

- 5.5 RS-422 / 107

- 5.6 Modems and Baud Rate / 108

- 5.7 Network Topologies / 109

- 5.8 Network Data Formats / 110

- 5.9 RS-485 / 112

- 5.10 A Simple RS-485 Network / 114

- 5.11 Interchip Serial Communications / 117

##

- 6.1 Evolution / 121

- 6.2 Motorola 6800 Eight-bit Microprocessor Family / 122

- 6.3 Intel 8051 Microcontroller Family / 125

- 6.4 Microchip PIC® Microcontroller Family / 131

- 6.5 Intel 8086 16-Bit Microprocessor Family / 134

- 6.6 Motorola 68000 16/32-Bit Microprocessor Family / 139

# PART 2 Advanced Digital Systems

#### Chapter 7 Advanced Microprocessor Concepts ......145

- 7.1 RISC and CISC / 145

- 7.2 Cache Structures / 149

- 7.3 Caches in Practice / 154

- 7.4 Virtual Memory and the MMU / 158

- 7.5 Superpipelined and Superscalar Architectures / 161

- 7.6 Floating-Point Arithmetic / 165

- 7.7 Digital Signal Processors / 167

- 7.8 Performance Metrics / 169

#

- 8.1 Synchronous DRAM / 173

- 8.2 Double Data Rate SDRAM / 179

- 8.3 Synchronous SRAM / 182

- 8.4 DDR and QDR SRAM / 185

- 8.5 Content Addressable Memory / 188

#

- 9.1 Protocol Layers One and Two / 193

- 9.2 Protocol Layers Three and Four / 194

- 9.3 Physical Media / 197

- 9.4 Channel Coding / 198

- 9.5 8B10B Coding / 203

- 9.6 Error Detection / 207

- 9.7 Checksum / 208

- 9.8 Cyclic Redundancy Check / 209

- 9.9 Ethernet / 215

| Chapter 10 | Logic Design and Finite State Machines | .221 |

|------------|----------------------------------------|------|

|------------|----------------------------------------|------|

- 10.1 Hardware Description Languages / 221

- 10.2 CPU Support Logic / 227

- 10.3 Clock Domain Crossing / 233

- 10.4 Finite State Machines / 237

- 10.5 FSM Bus Control / 239

- 10.6 FSM Optimization / 243

- 10.7 Pipelining / 245

#

- 11.1 Custom and Programmable Logic / 249

- 11.2 GALs and PALs / 252 11.3 CPLDs / 255

- 11.4 FPGAs / 257

# PART 3 Analog Basics for Digital Systems

| Chapter 12 Electrical Fundamentals      |  |

|-----------------------------------------|--|

| 12.1 Basic Circuits / 267               |  |

| 12.2 Loop and Node Analysis / 268       |  |

| 12.3 Resistance Combination / 271       |  |

| 12.4 Capacitors / 272                   |  |

| 12.5 Capacitors as AC Elements / 274    |  |

| 12.6 Inductors / 276                    |  |

| 12.7 Nonideal RLC Models / 276          |  |

| 12.8 Frequency Domain Analysis / 279    |  |

| 12.9 Lowpass and Highpass Filters / 283 |  |

| 12.10 Transformers / 288                |  |

|                                         |  |

|                                         |  |

|                                         |  |

| Chapter 13 Diodes and Transistors       |  |

| 14.1 The                 | 14 Operational Amplifiers                       |     |

|--------------------------|-------------------------------------------------|-----|

|                          | acteristics of Real Op-amps / 316               |     |

|                          | width Limitations / 324                         |     |

| 14.4 Input               | Resistance / 325                                |     |

| 14.5 Sum                 | nation Amplifier Circuits / 328                 |     |

| 14.6 Activ               | e Filters / 331                                 |     |

| 14.7 Com                 | parators and Hysteresis / 333                   |     |

| Chapter                  | 15 Analog Interfaces for Digital Systems        |     |

| -                        | ersion between Analog and Digital Domains / 339 |     |

|                          | ling Rate and Aliasing / 341                    |     |

| a set our set of the set | Circuits / 345                                  |     |

|                          | Circuits / 348                                  |     |

| 15.5 Filter              | s in Data Conversion Systems / 350              |     |

| PART                     | Digital System Design in Practice               |     |

| Chanter                  | 16 Clock Distribution                           |     |

| -                        | al Oscillators and Ceramic Resonators / 355     | •   |

|                          | Skew Clock Buffers / 357                        |     |

|                          | Delay Buffers: The PLL / 360                    |     |

|                          | ency Synthesis / 364                            |     |

|                          | /-Locked Loops / 366                            |     |

|                          | ze-Synchronous Clocking / 367                   |     |

| Chapter                  | 17 Voltage Regulation and Power Distribution    |     |

|                          | ge Regulation Basics / 372                      |     |

|                          | nal Analysis / 374                              |     |

|                          | r Diodes and Shunt Regulators / 376             |     |

|                          | sistors and Discrete Series Regulators / 379    |     |

|                          | ur Regulators / 382                             |     |

|                          | ching Regulators / 386                          |     |

| 17.7 Powe                | ar Distribution / 389                           |     |

| 17.8 Elect               | rical Integrity / 392                           |     |

| Chapter                  | 18 Signal Integrity                             |     |

| •                        | smission Lines / 398                            | •   |

|                          | ination / 403                                   |     |

|                          | stalk / 408                                     |     |

|                          | romagnetic Interference / 410                   |     |

|                          | nding and Electromagnetic Compatibility / 413   |     |

|                          | rostatic Discharge / 415                        |     |

|                          |                                                 |     |

| Chapter                  | 19 Designing for Success                        | ••• |

| 19.1 Prac                | ical Technologies / 420                         |     |

|                          | ed Circuit Boards / 422                         |     |

X

19.3 Manually Wired Circuits / 425

19.4 Microprocessor Reset / 428

19.5 Design for Debug / 429

19.6 Boundary Scan / 431

19.7 Diagnostic Software / 433

19.8 Schematic Capture and Spice / 436

19.9 Test Equipment / 440

Appendix A Further Education......443

Index 445